Designing and deploying real-time Digital Signal Processing (DSP) systems involves overcoming several technical hurdles. These challenges span hardware limitations, algorithmic constraints, and real-time performance requirements. Below are the key challenges and their implications:

1. Computational Complexity

Problem

DSP algorithms (e.g., FFT, adaptive filters, convolutional neural networks) require high-speed arithmetic operations (MACs—Multiply-Accumulates per second).

- Example: A 1024-point FFT requires ~10,240 MACs.

- Real-time constraints demand processing within strict time limits (e.g., audio at 44.1 kHz → ~22.7 µs per sample).

Solutions

✔ Optimized DSP libraries (e.g., ARM CMSIS-DSP, Intel IPP).

✔ Parallel processing (SIMD, VLIW architectures in DSP chips).

✔ Fixed-point arithmetic (reduces latency vs. floating-point).

2. Latency & Throughput Requirements

Problem

- Low-latency applications (e.g., active noise cancellation, motor control) require sub-millisecond response times.

- High-throughput systems (e.g., 5G basebands, video processing) need Giga-sample/sec handling.

Solutions

✔ Pipelining (breaks tasks into stages).

✔ Hardware acceleration (FPGA co-processors, GPU offloading).

✔ Block processing (trade-off between latency and efficiency).

3. Memory Constraints

Problem

- Limited on-chip RAM in embedded DSPs (e.g., TI C6000, STM32H7).

- Memory bottlenecks when accessing external SDRAM.

Solutions

✔ Cache optimization (DMA for data transfers).

✔ Circular buffers (efficient real-time data handling).

✔ Memory-efficient algorithms (e.g., in-place FFT).

4. Power Consumption

Problem

- Battery-powered devices (e.g., wearables, IoT sensors) need ultra-low-power DSP.

- High-performance DSPs (e.g., for radar) may consume Watts of power.

Solutions

✔ Clock gating (disable unused cores).

✔ Dynamic voltage/frequency scaling (DVFS).

✔ Approximate computing (trade precision for power savings).

5. Real-Time Operating System (RTOS) Challenges

Problem

- Deterministic scheduling is critical (missed deadlines cause failures).

- Interrupt jitter can disrupt signal processing.

Solutions

✔ Preemptive RTOS (FreeRTOS, Zephyr).

✔ Interrupt prioritization (NVIC settings in ARM Cortex-M).

✔ Hardware timers for precise sampling.

6. Numerical Precision & Stability

Problem

- Fixed-point quantization errors (overflow, rounding).

- Algorithm instability (e.g., IIR filters may diverge).

Solutions

✔ Saturation arithmetic (prevents overflow).

✔ Adaptive filtering (LMS, RLS for dynamic environments).

✔ Error analysis (simulate in MATLAB/Python first).

7. Hardware-Software Co-Design

Problem

- Algorithm selection affects hardware choice (DSP vs. FPGA vs. GPU).

- Bottlenecks in data movement (e.g., CPU ↔ FPGA).

Solutions

✔ HLS (High-Level Synthesis) for FPGAs (Xilinx Vitis, Intel HLS).

✔ Heterogeneous computing (ARM + DSP + FPGA).

8. Real-World Noise & Non-Idealities

Problem

- Sensor noise (ADC quantization, thermal noise).

- Non-linearities (e.g., microphone distortion).

Solutions

✔ Kalman filtering (for noisy measurements).

✔ Calibration routines (correct sensor biases).

9. Debugging & Verification

Problem

- Real-time debugging is hard (no pause/resume).

- Reproducing field issues in the lab.

Solutions

✔ JTAG/SWD tracing (ARM ETM, Segger RTT).

✔ Data logging (stream to PC for post-analysis).

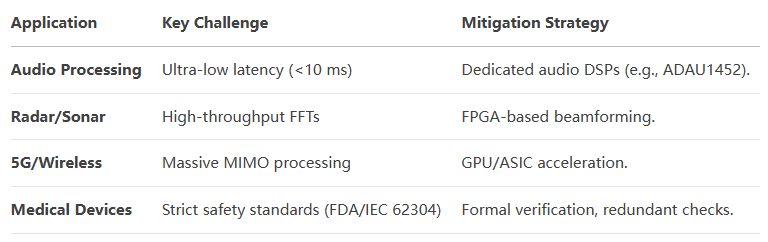

10. Industry-Specific Challenges

Conclusion

Implementing real-time DSP systems requires balancing:

- Speed vs. Power

- Precision vs. Complexity

- Flexibility vs. Determinism

Best Practices: